PCI-SIG Demonstrates PCIe 6.0 Interoperability at FMS 2024

As PCIe 5.0 adoption gains momentum in both the data center and consumer markets, PCI-SIG is not sitting idle and is already working to prepare the ecosystem for PCIe specification updates. At FMS 2024, some vendors even talked about PCIe 7.0 with its 128 GT/s capabilities, even though PCIe 6.0 hasn’t even started shipping yet. We reached out to PCI-SIG to get an update on its activities and discuss the current state of the PCIe ecosystem.

PCI-SIG has already made the PCIe 7.0 specification (version 0.5) available to its members and expects the full specifications to be officially released sometime in 2025. The goal is to provide data transfer rates of 128 GT/s with bi-directional speeds of up to 512 GB/s. traffic via x16 links. Similar to PCIe 6.0, this specification will also use PAM4 signaling and maintain backward compatibility. Energy efficiency and silicon die area were also taken into account when developing the design.

The transition to PAM4 signaling results in a higher bit error rate compared to the previous NRZ scheme. This has led to the need to adopt a different error correction scheme in PCIe 6.0—instead of working with variable-length packets, PCIe 6.0 flow control module (FLIT) coding works with fixed-size packets to aid in forward error correction. PCIe 7.0 retains these aspects.

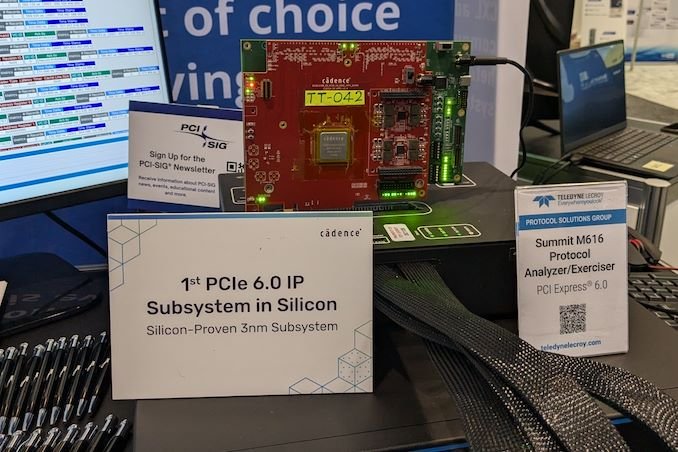

The list of PCIe 6.0 compliance program integrators is expected to be published in 2025, although initial testing is already underway. This was evident in the FMS 2024 demo, which used Cadence’s 3nm test chip for its PCIe 6.0 IP offering, as well as Teledyne Lecroy’s PCIe 6.0 analyzer. These timings align well with the specification completion dates and compliance program availability for previous generations of PCIe.

We also received an update on the Optical Working Group: While independent from optical technologies, the working group also intends to develop form factors for specific technologies, including pluggable optical transceivers, embedded optics, co-packaged optics, and optical I/O. The logical and electrical layers of the PCIe 6.0 specification are being refined to meet the new PCIe optical standardization, a process that will also be followed with PCIe 7.0 to coincide with the standard’s release next year.

PCI-SIG also has ongoing cabling initiatives. On the consumer side, we are seeing significant popularity in Thunderbolt and external GPU enclosures. However, even data centers and enterprise systems are moving to cable solutions as it becomes clear that separating components such as storage from the CPU and GPU is better for thermal design. Additionally, maintaining signal integrity over long distances becomes difficult for onboard signal traces. This is where internal cabling of computer systems can help.

OCuLink turned out to be a good candidate and has become quite widely used as an internal link in server systems. It has even appeared in mini PCs from some Chinese manufacturers as an external avatar for the consumer market, albeit with limited popularity. As speeds increase, a widely accepted standard for external PCIe peripherals (or even for connecting components within a system) will become mandatory.

2024-08-15 20:30:00